# IDEС 참여 매뉴얼

## - 참여교수 배포용 -

2026.02

반도체설계교육센터

IC DESIGN EDUCATION CENTER

## 목 차

|                                                                  |    |

|------------------------------------------------------------------|----|

| 참여교수 신청 .....                                                    | 2  |

| 1. 개요 .....                                                      | 2  |

| 2. 지원 사항 .....                                                   | 2  |

| 3. 신청 시기 .....                                                   | 2  |

| 4. 신청 조건 .....                                                   | 2  |

| 5. 참여교수 의무사항 .....                                               | 2  |

| 6. 선정 방법 .....                                                   | 3  |

| 7. 선정 제외 대상 .....                                                | 3  |

| 8. 신청 절차 .....                                                   | 4  |

| 9. 우수 참여교수 선정 .....                                              | 13 |

| 10. 우수 연구교수 선정 .....                                             | 14 |

| <br>MPW 참여 안내 .....                                              | 15 |

| 1. MPW 참가 대상 및 설계 참여시 이행 사항 .....                                | 15 |

| 2. 2026년 MPW 지원 내역 및 일정 .....                                    | 20 |

| 3. MPW 참여 방법 .....                                               | 23 |

| 4. 참여방법(지정공정) .....                                              | 27 |

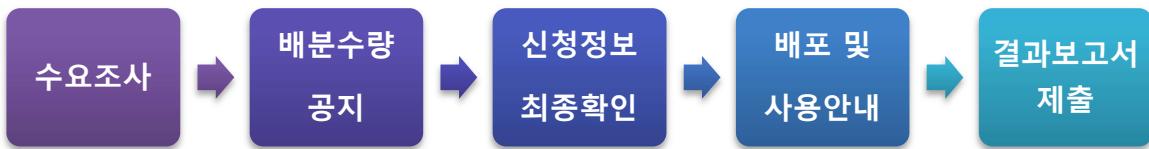

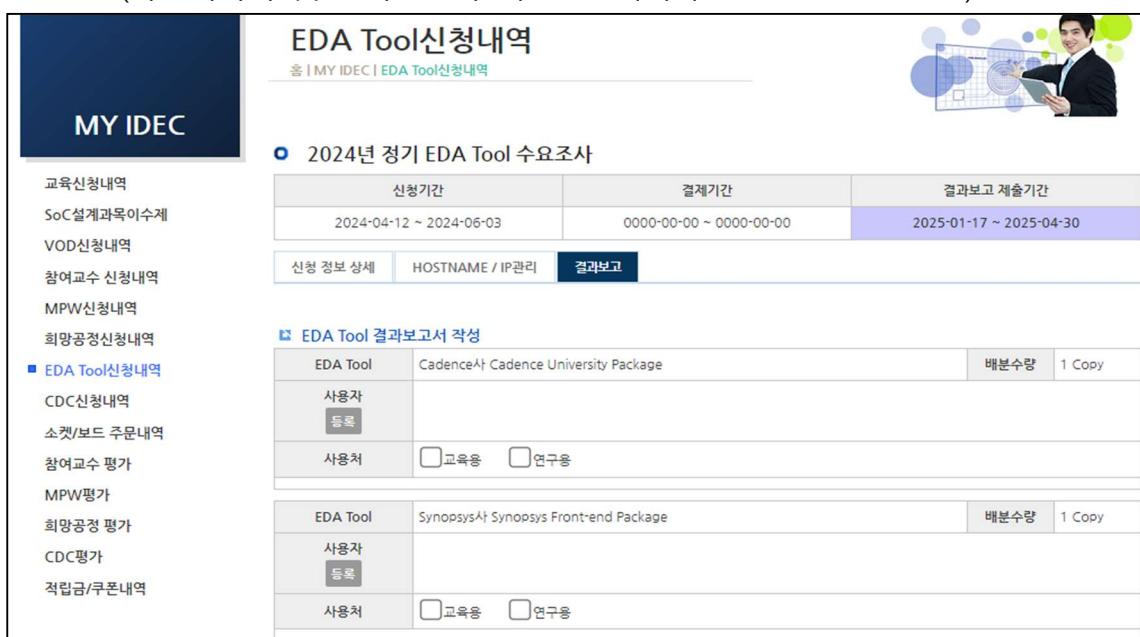

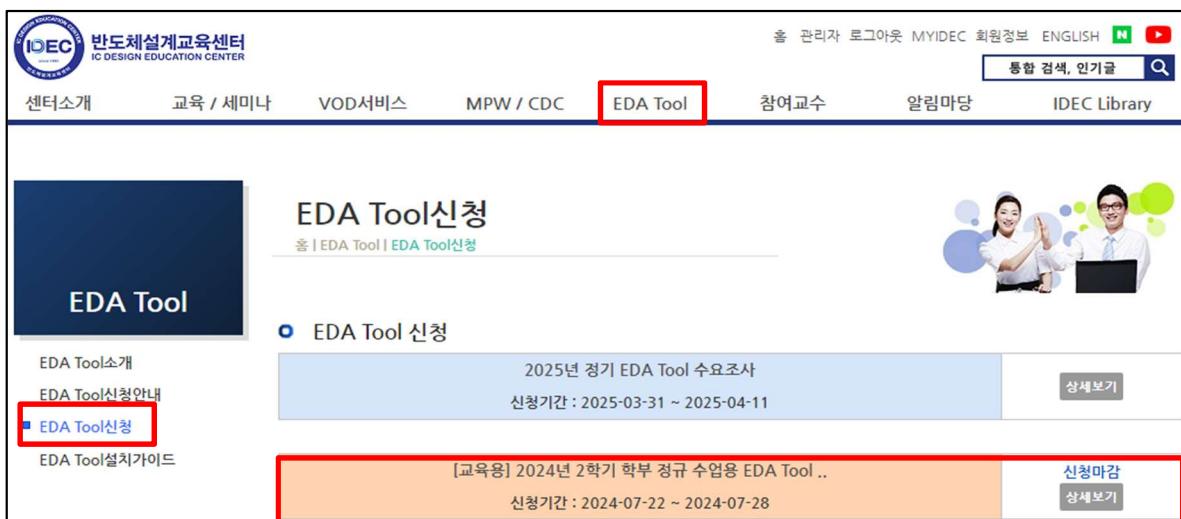

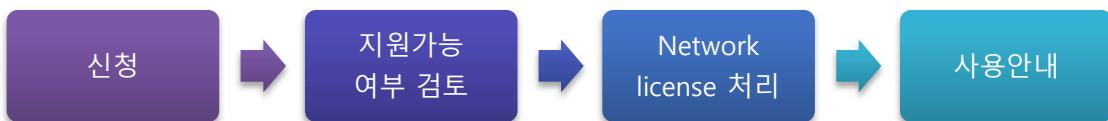

| <br>EDA Tool 사용 안내 .....                                         | 38 |

| 1. 개요 및 지원현황 .....                                               | 38 |

| 2. 지원방식 .....                                                    | 41 |

| 3. 정규 연구용 라이선스 사용 .....                                          | 41 |

| 4. 정규 수업용(교육용) 라이선스 사용 .....                                     | 45 |

| 5. Network License 사용 .....                                      | 49 |

| 6. EDA Tool 지원 서비스 .....                                         | 50 |

| <br>CDC [Chip Design Contest] .....                              | 53 |

| 1. CDC 소개 .....                                                  | 53 |

| 2. CDC 참여 절차 .....                                               | 54 |

| 3. CDC 평가 .....                                                  | 59 |

| <br>JICAS (IDEC Journal of Integrated Circuits and System) ..... | 60 |

| 1. JICAS 소개 .....                                                | 60 |

| 2. JICAS 진행 절차 .....                                             | 60 |

1

## 참여교수 신청

### 1. 개요

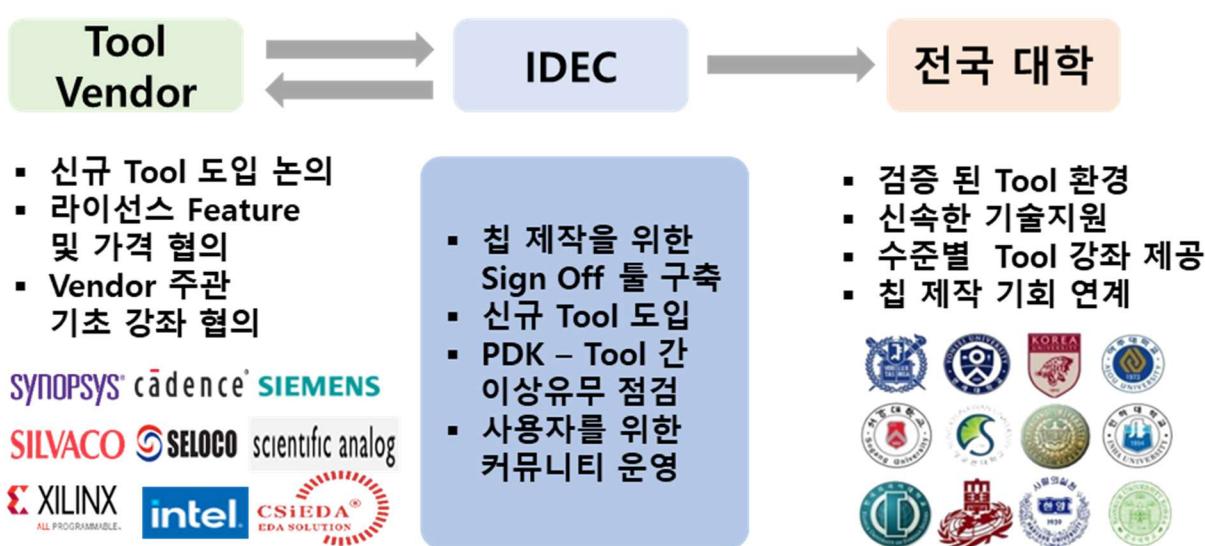

- 1) 차세대시스템반도체 전문인력 양성과 핵심 IP연구개발을 위해 다각적인 전국 대학의 교수를 참여교수로 선정하여 칩제작기회(MPW) 및 설계환경(EDA Tool) 등 지원

- 2) 반도체설계 분야의 연구 경쟁력을 확보하기 위해 참여교수의 유사 연구 분야를 조사하여 연구분야 특성화를 제공

### 2. 지원 사항

- 1) 최신 기술 공정의 MPW 칩 제작 지원(Cell Library 포함)

- 2) 최신 EDA Tool 지원

- 3) IDEC 보유 Analog IP 제공

### 3. 신청 시기

- 1) 년 1회 (매년 2월 모집)

### 4. 신청 조건

- 1) 전국 대학의 반도체설계 관련분야 교수 (전임직 조교수부터 신청 가능)

- 2) 단, 순수 교육 및 연구 목적이 아닌 특수목적 대학소속의 교수의 경우 IDEC 지원이 제한됨 (참고 : 전문대학의 경우, IDEC 지원이 제한 될 수 있음)

### 5. 참여교수 의무사항

- 1) "IDECK 주최 행사(Congress)"에 **2년에 1회 이상 반드시 참여**한다.

- 2) IDEC에서 협조하는 사항(뉴스레터 원고 기고 또는 명예기자 추천, JICAS 논문 제출(분기 별) 또는 인용, JICAS 편집위원 또는 리뷰어 활동, IDEC 관련 평가(C.D.C(2,7,10월), IDEC 강좌 강사 활동 등)에 대해 **3년 이내 1회 이상 참여** 한다.

- 3) IDEC 지원을 받아 달성한 **연구실적(논문, 특허, 지도학생 취업현황 등)**은 IDEC에 보고 한다.

\* IDEC 참여교수로 활동 시에 위의 세가지 사항 모두 이행을 부탁드립니다.

### [참고 내용]

- IDEC Congress : 참여대학의 주요실적에 대한 결과 발표 및 현안 논의가 이뤄지는 IDEC 주관 행사로, 참여교수는 본 행사에 **2년에 1회 이상 필수 참석 (대리 참석 불가)**

- JICAS : 매년 4회 발행되는 IDEC 공식 국제 저널인 JICAS에 MPW 칩 설계 결과물을 논문으로 작성하여 제출 (논문 상시 접수)

- CDC : IDEC CDC 행사에 제출된 논문의 채택 여부를 결정하기 위해 온라인 평가 진행 (매년 IDEC CDC 평가위원 위촉)

- IDEC 교육 : 본센터(KAIST)와 6개 캠퍼스에서 연간 150 건 정도의 설계 및 Tool 교육 등이 개설/진행되고 있으며, 이에 주도적으로 강의 개설

- IDEC 사사문구 : IDEC의 지원을 받아 발행된 논문에는 반드시 IDEC 지원(MPW, EDA Tool) 사사문구 기재, \*\*Acknowledgement(감사의 글)에 포함되어도 실적 인정

| 구분 |                           | 사사문구 예시                                                                                           |

|----|---------------------------|---------------------------------------------------------------------------------------------------|

| 국문 | MPW 지원받은 경우               | 본 연구는 IDEC에서 MPW를 지원받아 수행하였습니다.                                                                   |

|    | EDA Tool 지원받은 경우          | 본 연구는 IDEC에서 EDA Tool을 지원받아 수행하였습니다.                                                              |

| 영문 | MPW 지원받은 경우               | The chip fabrication was supported by the IC Design Education Center(IDECK), Korea.               |

|    | EDA Tool 지원받은 경우          | The EDA tool was supported by the IC Design Education Center(IDECK), Korea.                       |

|    | MPW 와 EDA Tool 모두 지원받은 경우 | The chip fabrication and EDA tool were supported by the IC Design Education Center(IDECK), Korea. |

## 6. 선정 방법

- 1) 기존 참여교수 : 전년도 참여계획 및 의무사항 이행, IDEC이 인정하는 실적 제출시 선정

- 2) 신규 참여교수 : 신청서 및 이력서를 토대로 IDEC 평가를 통해 선정

## 7. 선정 제외 대상

- 1) 기존 참여교수 : 참여교수 의무사항을 이행하지 않거나, 최근 3년간 IDEC에서 인정하는 실적을 제출하지 않은 자

- 2) 신규 참여교수 : 신청조건에 불충족하거나, IDEC 평가시 미승인된 자

- 3) 비전임 교수

## 8. 신청 절차

### 1) 신규 및 기존 참여교수

- ① www.idec.or.kr 로그인 -> 참여교수 클릭

KAIST IDEC

공지사항 Notice

- [IDECK] 2024년 참여교수 배출.. 2025.01.13

- [IDECK] 2025년 1학기 학부 정.. 2025.01.13

- [IDECK MPW] 2025년 IDEC MPW .. 2024.12.18

- [IDECK] 제8기 시스템반도체.. 2024.11.11

- [외부공지] [외부공지] 차세.. 2024.12.30

자료실 Library

- EDA Tool Vendor 의 Syste.. 2024.12.16

- EDA Tool Vendor 의 Syste.. 2024.04.01

- EDA Tool Vendor 의 Syste.. 2023.09.12

- EDA Tool Vendor 의 Syste.. 2023.01.27

- [CADENCE] INDAGO - Debug.. 2022.10.04

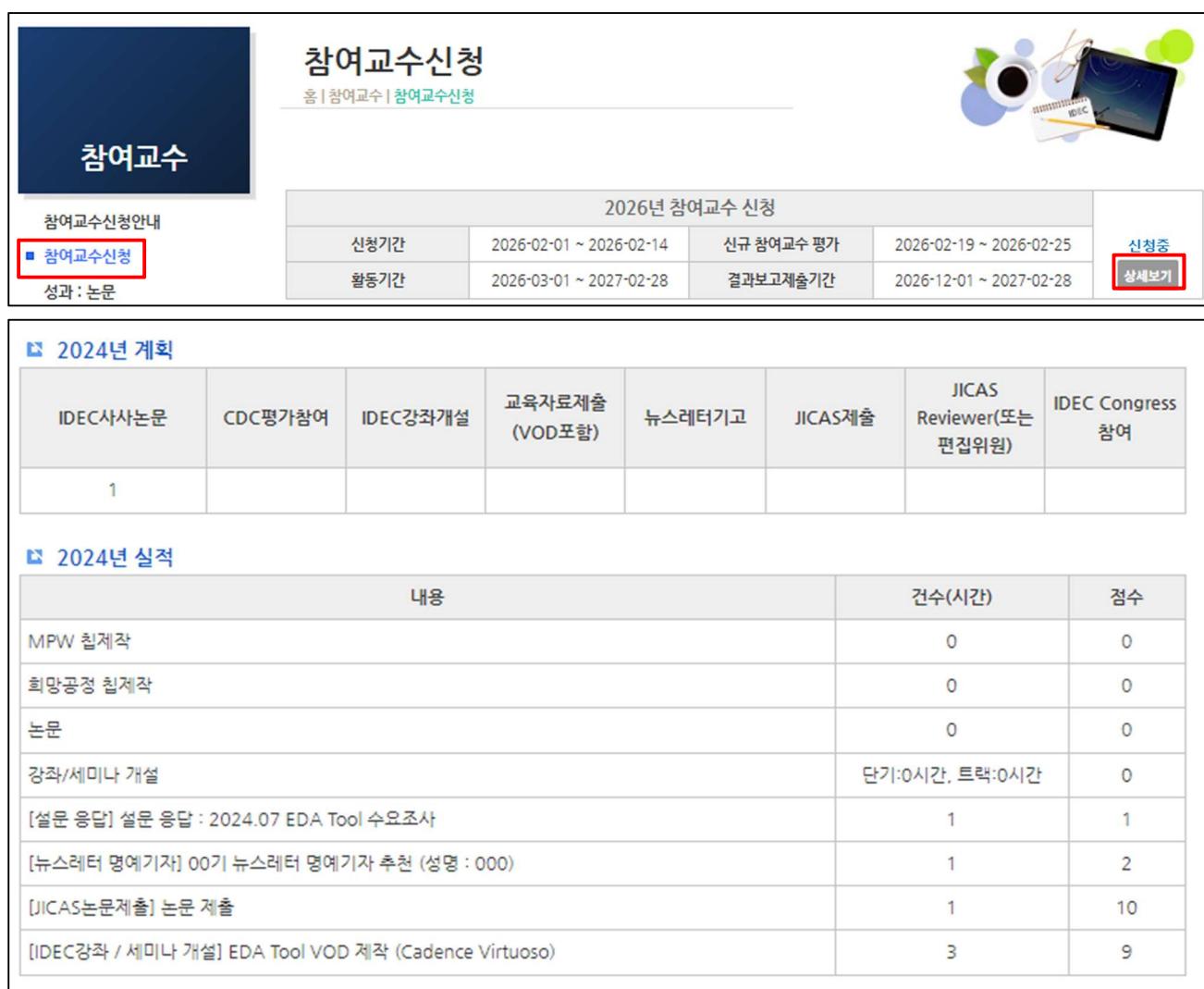

- ② 참여교수 신청 클릭 -> 상세보기 -> 참여신청

참여교수신청

2026년 참여교수 신청

| 신청기간 | 2026-02-01 ~ 2026-02-14 | 신규 참여교수 평가 | 2026-02-19 ~ 2026-02-25 |

|------|-------------------------|------------|-------------------------|

| 활동기간 | 2026-03-01 ~ 2027-02-28 | 결과보고제출기간   | 2026-12-01 ~ 2027-02-28 |

2024년 계획

| IDECK사사논문 | CDC평가참여 | IDECK강좌개설 | 교육자료제출<br>(VOD포함) | 뉴스레터기고 | JICAS제출 | JICAS<br>Reviewer(또는<br>편집위원) | IDECK Congress<br>참여 |

|-----------|---------|-----------|-------------------|--------|---------|-------------------------------|----------------------|

| 1         |         |           |                   |        |         |                               |                      |

2024년 실적

| 내용                                                    | 건수(시간)         | 점수 |

|-------------------------------------------------------|----------------|----|

| MPW 칩제작                                               | 0              | 0  |

| 희망공정 칩제작                                              | 0              | 0  |

| 논문                                                    | 0              | 0  |

| 강좌/세미나 개설                                             | 단기:0시간, 트랙:0시간 | 0  |

| [설문 응답] 설문 응답 : 2024.07 EDA Tool 수요조사                 | 1              | 1  |

| [뉴스레터 명예기자] 00기 뉴스레터 명예기자 추천 (성명 : 000)               | 1              | 2  |

| [JICAS논문제출] 논문 제출                                     | 1              | 10 |

| [IDECK강좌 / 세미나 개설] EDA Tool VOD 제작 (Cadence Virtuoso) | 3              | 9  |

③ 참여교수 신청서 작성

- **지도학생 기입** : 전년도 지도학생 중 졸업생을 제외한 재학생은 자동으로 등록된다. 신규 지도학생을 추가할 수 있으며, **실무 담당자를 선택한다.**

- 2026년 2월 졸업예정인 학생도 등록을 해야 2027년 2월에 2026년 참여교수 배출인력 실적으로 기입할 수 있다.

- **파란색+** : 지도 학생 추가 / **빨간색X** :지도학생 삭제

- **주요 연구분야 기입** : 주요 연구분야는 아래 항목 중 1개를 필수로 선택한다. 추가로 명시해야할 다른 연구분야가 있으면 '주요 연구분야 2'로 선택가능하다.

| 구분          | 연구분야      | 구분          | 연구분야 |

|-------------|-----------|-------------|------|

| 회로 및 시스템 설계 | 디지털 회로    | 공정 및 소자     | 공정   |

|             | 아날로그 회로   |             | 소자   |

|             | RF 회로     | 패키징         |      |

|             | Mixed 회로  | EDA 및 소프트웨어 |      |

|             | Power 회로  | 기타          |      |

|             | SOC 및 시스템 |             |      |

|             | 기타        |             |      |

\* 'SOC 및 시스템' : 최소 수천개에서 수십만개의 게이트 집적을 뜻함

- **특성화 분야 작성** : 작성버튼을 클릭하면 등록 또는 수정이 가능

- 가로와 세로가 만나는 셀을 선택(최대 6개)한 후 등록 및 수정완료 버튼을 클릭한다.

# IDECA Manual(참여교수)

| ▶ SoC 설계 방법 및 구조 |                                         |                  | Digital           |                        | Design methodology | Analog/RF       |                               |    |       |       |

|------------------|-----------------------------------------|------------------|-------------------|------------------------|--------------------|-----------------|-------------------------------|----|-------|-------|

| ▼ 등용분야           | 대분류                                     | 중분류              | Programmable core | Special function block |                    | Data Converters | Timing & High-Speed Interface | RF | Power | 기타 IP |

| Consumer         | 대형 Media(TV 등)                          |                  |                   |                        |                    |                 |                               |    |       |       |

|                  | Handheld Multimedia                     |                  |                   |                        |                    |                 |                               |    |       |       |

|                  | Display (LCD/OLED/PDP/display Driver 등) |                  |                   |                        |                    |                 |                               |    |       |       |

| Car/Robot        | Car infotainment (navi/audio/DMB)       |                  |                   |                        |                    |                 |                               |    |       |       |

|                  | Car chassis(brake/suspension/steering)  |                  |                   |                        |                    |                 |                               |    |       |       |

|                  | Body/security(출출방지 등)                   |                  |                   |                        |                    |                 |                               |    |       |       |

| Communication    | Robot                                   |                  |                   |                        |                    |                 |                               |    |       |       |

|                  | Wired                                   | Level 2/3 switch |                   |                        |                    |                 |                               |    |       |       |

|                  |                                         | MODEM            |                   |                        |                    |                 |                               |    |       |       |

|                  |                                         | Access network   |                   |                        |                    |                 |                               |    |       |       |

|                  |                                         | PAN              |                   |                        |                    |                 |                               |    |       |       |

|                  | Wireless(무선통신)                          | LAN/MAN/WAN/CAN  |                   |                        |                    |                 |                               |    |       |       |

|                  |                                         | USN/RFID         |                   |                        |                    |                 |                               |    |       |       |

|                  |                                         | Wiimax,WiBro,LTE |                   |                        |                    |                 |                               |    |       |       |

|                  |                                         | Celluar phone    |                   |                        |                    |                 |                               |    |       |       |

|                  |                                         | Ubiquitous       |                   |                        |                    |                 |                               |    |       |       |

| 신 재생 에너지         | Military/Space                          |                  |                   |                        |                    |                 |                               |    |       |       |

|                  | Energy Harvesting(태양광/열전 등)             |                  |                   |                        |                    |                 |                               |    |       |       |

|                  | Energy Storage(배터리 등)                   |                  |                   |                        |                    |                 |                               |    |       |       |

| Medical/Bio      | Energy transfer System(Grid 등)          |                  |                   |                        |                    |                 |                               |    |       |       |

|                  | Medical/Bio                             |                  |                   |                        |                    |                 |                               |    |       |       |

|                  | 분류되지 않은 기타                              |                  |                   |                        |                    |                 |                               |    |       |       |

\*\* 가로와 세로가 만나는 셀을 선택(최대6개)하시고 등록 및 수정 완료 버튼을 클릭해주세요\*\*\*

- 특성화 자료 활용동의여부 체크 후 페이지 하단 확인 버튼을 클릭한다.

## ○ 참여교수 특성화 등록시 아래 사항을 확인하세요.

### ▣ 기본자료 활용 동의

\*참여교수 특성화 (Platform) 구축에 기본 자료로 활용\* 하는 것에 동의하십니까?

예. 동의 합니다.

### ▣ 개인정보 정책

"참여교수 특성화 (Platform) 웹페이지에 기본정보(소속, 성명, 연락처, E-mail), 일반정보(연구분야)등 정보제공"에 동의하십니까?

예. 동의 합니다.  아니오. 동의하지 않습니다.

- **연구분야 상세** : 연구분야 및 IDEC에서 활동 가능한 분야에 대해 보다 상세히 입력한다.

|          |  |

|----------|--|

| 연구 분야 상세 |  |

|----------|--|

## IDECA Manual(참여교수)

- 금년도 참여계획 : 참여교수 의무사항 항목이며, 참여계획 건수를 입력한다.

- 이력서 : 신규참여 교수의 경우 이력서 등록(필수)

- 입력란을 모두 기입하고 참여교수 수행 지침 등의 후 참여신청 클릭

|                |                                                                                                                                                                                                                                                                     |     |                                                                                                      |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------------------------------------------------------------------------------------------------|

| 금년도<br>참여계획    | 항목                                                                                                                                                                                                                                                                  | 건수  | 설명                                                                                                   |

|                | IDECA사사논문                                                                                                                                                                                                                                                           | 1 건 | IDECA의 지원을 받아 발행된 논문에는 반드시 IDECA 사사문구를 기입해야 하며, 해당 실적은 참여교수 실적으로 포함                                  |

|                | IDECA강좌개설                                                                                                                                                                                                                                                           | 2 건 | 본센터(KAIST)와 6개 캠퍼스에서 연간 150건 정도의 설계 및 Tool교육 강좌를 운영하고 있으며, IDECA 강좌 개설 또는 강의 진행                      |

|                | 교육VOD제작<br>참여                                                                                                                                                                                                                                                       | 3 건 | EDA Tool 강의 등 VOD 전용 강좌 제작 및 업로드에 동의                                                                 |

|                | JICAS논문제작                                                                                                                                                                                                                                                           | 4 건 | 매년 4회 발행되는 IDECA 공식 국제 저널인 JICAS에 MPW 칩 설계 결과물 (또는 칩 설계 관련 내용)을 논문으로 작성하여 제출 및 게재 (논문 상시 접수)         |

|                | JICAS Reviewer<br>(또는 편집위원)                                                                                                                                                                                                                                         | 5 건 | JICAS에 투고된 논문을 온라인 저널 시스템에서 심사하고 게재 여부 결정                                                            |

|                | IDECA<br>Congress참여                                                                                                                                                                                                                                                 | 6 건 | 참여대학의 주요실적에 대한 결과 발표 및 현안 논의가 이뤄지는 IDECA 주관 행사로, 참여교수는 본 행사에 2년에 1회 이상 참석 의무가 있음.                    |

|                | 뉴스레터기고                                                                                                                                                                                                                                                              | 7 건 | 매년 4회 발행되는 IDECA 뉴스레터에 반도체 설계와 관련된 기술 동향 또는 연구 분야, 학회 참가 후기, 반도체 인력 양성과 관련한 칼럼 등을 작성하여 제출 (원고 상시 접수) |

|                | 뉴스레터<br>명예기자 추천                                                                                                                                                                                                                                                     | 8 건 | IDECA 뉴스레터 명예기자 추천                                                                                   |

|                | CDC평가참여                                                                                                                                                                                                                                                             | 9 건 | 1년에 3회 IDECA CDC 행사에 제출된 논문의 채택 및 수상 여부를 결정하기 위해 무료로 온라인 평가 진행 (임기 1년)                               |

| 가입목적           | <input checked="" type="checkbox"/> MPW 참가 <input checked="" type="checkbox"/> EDA Tool 사용 <input type="checkbox"/> 기타                                                                                                                                              |     |                                                                                                      |

| 이력서            | <small>* 신규 참여교수의 경우 이력서를 등록해야 합니다. (자유양식)</small><br><input type="button" value="파일선택"/> 선택된 파일 없음                                                                                                                                                                 |     |                                                                                                      |

| 참여교수<br>수행지침등의 | <small>제1조(사업 목표 및 내용)</small><br>참여교수의 사업 목표와 내용은 "참여교수 지원 신청서" 내용과 동일하다.<br><small>제2조(사업의 수행)</small><br>본 사업을 제1조의 "참여교수 지원 신청서" 상의 내용에 따라 수행한다.<br><small>제3조(자원의 지원)</small><br>(1) 본 사업의 수행을 위해 IDECA는 참여교수에게 EDA Tool, MPW(Multi Project Wafer) 칩제작 공정 등의 자 |     |                                                                                                      |

|                | <input checked="" type="checkbox"/> 참여교수 수행 지침에 동의합니다.                                                                                                                                                                                                              |     |                                                                                                      |

|                | <input type="button" value="이전으로"/>                                                                                                                                                                                                                                 |     | <input type="button" value="참여신청"/>                                                                  |

### ① 참여교수 신청 완료

|      |         |            |

|------|---------|------------|

| 제목   | 참여교수 신청 |            |

| 신청기간 |         | 신규 참여교수 평가 |

| 활동기간 |         | 결과보고제출기간   |

- 기존 참여교수의 경우 성과물을 제출해주세요. 성과물을 제출하지 않을 경우 MPW, EDA Tool 지원이 제한될 수 있습니다.

## ④ 최종선정안내

- 기존 참여교수 : 신청 후 선정 안내 이메일 발송

- 신규 참여교수 : 내부 평가 진행 후 최종 선정 안내 이메일 발송 예정.

## 2) 제출 항목 (기존 참여교수만)

### ① 인력배출 현황 작성

- MYIDEC > 참여교수 신청내역 > 2024년 참여교수 클릭

- 2025년도 2, 8월 졸업생의 취업현황을 제출 \* 취업/진학 구분을 명확히 기재

전년도 졸업생 중 취업현황에 변동이 있으면 반드시 수정 **(IDECK 중요 실적자료로 활용되므로 졸업학위, 취업기관 등 정확한 기재를 부탁드립니다.)**

| 2025년 참여교수 신청                                                                                                                                                                                                                                  |                         |                                                                                                                                                                                                                                                |                         |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|

| 신청기간                                                                                                                                                                                                                                           | 신규참여교수 평가               | 활동기간                                                                                                                                                                                                                                           | 결과보고 제출기간               |  |  |

| 2025-02-03 ~ 2025-02-28                                                                                                                                                                                                                        | 2025-02-17 ~ 2025-03-19 | 2025-02-19 ~ 2026-02-28                                                                                                                                                                                                                        | 2025-12-01 ~ 2026-02-28 |  |  |

| 신청 정보 상세                                                                                                                                                                                                                                       |                         | <input style="background-color: #0070C0; color: white; border: 1px solid #0070C0; padding: 5px; margin-right: 10px;" type="button" value="결과 보고 제출"/> <input style="border: 1px solid #0070C0; padding: 5px;" type="button" value="결과 보고 제출"/> |                         |  |  |

| <input style="border: 1px solid #0070C0; padding: 5px; margin-right: 10px;" type="button" value="신청 정보 상세"/> <input style="background-color: #0070C0; color: white; border: 1px solid #0070C0; padding: 5px;" type="button" value="결과 보고 제출"/> |                         |                                                                                                                                                                                                                                                |                         |  |  |

| 2025년도 결과보고 (졸업/취업 현황) 제출                                                                                                                                                                                                                                |      |      |      |                    |                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|--------------------|-----------------|

| 인력배출 현황 (2025년 2월, 8월 졸업자)                                                                                                                                                                                                                               |      |      |      |                    |                 |

| <ul style="list-style-type: none"> <li>지도 학생 중 졸업생이 있을 경우 학위,지도교수,졸업년월,취업기관,부서명을 기입하신후 [적용]버튼을 클릭해주십시오.</li> <li>졸업생이 없을 경우에도 [적용] 버튼을 클릭하셔야 합니다.</li> <li>"졸업자구분" 항목 중 <b>재직</b> 중 <b>(직장인)</b>은 학위 시작 전 취업한 학생을 말하며, 이외는 신입(일반)으로 선택해 주십시오.</li> </ul> |      |      |      |                    |                 |

| 성명                                                                                                                                                                                                                                                       | 졸업학위 | 지도교수 | 졸업년월 | 졸업자 구분<br>취업/진학 기관 | 취업/진학 구분<br>부서명 |

- 수행지침동의서 제출

| 참여교수신청                                                                                                                                                                                                                                                                                                                                                                  |  | 참여교수수행 지침 동의서                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| <b>참여교수</b><br><small>참여교수신청안내</small> <ul style="list-style-type: none"> <li>참여교수신청</li> <li>참여교수성과1<br/>성과::논문</li> <li>성과::IP</li> <li>성과::특허</li> </ul>                                                                                                                                                                                                             |  | <p>“한국 반도체산업의 경쟁력”<br/>IDECK에서 설계인력양성의 발판을 마련하겠습니다.</p>  <ul style="list-style-type: none"> <li>사업명 : 지능형반도체 전문인력양성 사업</li> <li>사업기간 : 2019년 3월 1일 ~ 2020년 2월 29일</li> <li>총괄 책임자 : 반도체설계교육센터 소장 박인철</li> <li>참여교수 : KAIST 교수 테스트</li> <li>본 수행지침 등에서는 “반도체설계교육센터(이하 IDEC)” 참여교수 협약 체결을 대신한다.</li> <li>참여교수 선정 시 관련 법적 책임은 본인에게 있으므로, 아래 내용을 검토하여 승인하도록 한다.</li> </ul> |  |

| <p>제9조(개인 정보 사용 동의)</p> <p>참여교수는 “참여교수 지원 신청서”의 내용을 실적보고 등 필요에 따라 관계 기관에 제공됨에 동의한다.</p> <p><input type="checkbox"/> 위의 모든 내용에 동의합니다.</p> <p style="text-align: center;"> <input style="border: 1px solid #0070C0; padding: 5px; margin-right: 10px;" type="button" value="확인"/> <input style="border: 1px solid #0070C0; padding: 5px;" type="button" value="취소"/> </p> |  |                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

## ② 성과 제출

- 해당기간 : 전년도 3월 1일~당해년도 2월 28일

- 해당기간의 성과를 IDEC 홈페이지 성과 제출 게시판에 업로드

- 제출 시기 : (참여교수 신청 기간 외에도) 수시 제출 가능

- 제출 방법

- 참여교수성과 탭에서 해당 실적 게시판 클릭

- 작성 완료후 수정사항이 있을시 수정가능

- 제출 내용 : 논문, 특허, IP, JICAS Citation

- IDEC 사사 논문은 참여교수 실적 점수로 인정되며, 추후 우수 기여상, 우수 연구상 선정시 반영

### [제출 항목 및 배점 대상 구분표]

| 항목 | 분류                                                             | 제출 내용                                                                                                                                                               | 배점대상 |

|----|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 논문 | IDECK 지원받았으며, IDECK 지원을 통한 결과물 및 사사문구 기재, 감사의 글에 지원 내용 표기 있음.  | <ul style="list-style-type: none"> <li>• 논문/저널명 풀네임으로 기입</li> <li>• (Published된 경우) 출판일 기입</li> <li>• IDEC 사사문구가 들어간 페이지번호 기입</li> <li>• 논문 전체 첨부파일로 업로드</li> </ul> | ○    |

|    | IDECK 지원받았으나, IDECK 지원을 통한 결과물 및 사사문구 기재, 감사의 글에 지원 내용 표기가 없음. | <ul style="list-style-type: none"> <li>• 논문/저널명 풀네임으로 기입</li> <li>• (Published된 경우) 출판일 기입</li> </ul>                                                               | ×    |

|    | IDECK 지원받지 않음                                                  | <ul style="list-style-type: none"> <li>• 논문/저널명 풀네임으로 기입</li> <li>• (Published된 경우) 출판일 기입</li> </ul>                                                               | ×    |

| 특허 | IDECK 지원                                                       | <ul style="list-style-type: none"> <li>• 출원증이나 등록증 첫장만 업로드</li> </ul>                                                                                               | ×    |

|    | IDECK 미지원                                                      |                                                                                                                                                                     |      |

| IP | IDECK 지원                                                       | <ul style="list-style-type: none"> <li>• 등록기관과 등록내역이 함께 캡처된 파일 업로드</li> </ul>                                                                                       | ×    |

|    | IDECK 미지원                                                      |                                                                                                                                                                     |      |

- 논문(입력 항목 화면)

반도체설계교육센터

IC DESIGN EDUCATION CENTER

센터소개 교육/세미나 VOD서비스 MPW EDA Tool 참여교수 홍보마당 IDEC Library

성과::논문

“한국 반도체산업의 경쟁력” IDEC에서 설계인력양성의 발판을 마련하겠습니다.

참여교수신청안내

참여교수신청

■ 참여교수성과

■ 성과::논문

성과::IP

성과::특허

| 논문제목                                                                                         | Algorithm for Synthesis and Exploration of Clock Spines |       |                  | 등록일 |

|----------------------------------------------------------------------------------------------|---------------------------------------------------------|-------|------------------|-----|

| ID                                                                                           | tkim                                                    | 작성자   | 2017.08.04 11:32 |     |

| 국외/국내                                                                                        | 국외                                                      | SCI구분 | 비SCI             |     |

| 학회/저널                                                                                        | 학회                                                      | 논문집명  | ASP-DAC          |     |

| IDECA지원여부                                                                                    | IDECA지원-ACK없음                                           | 지원내역  | EDA Tool         |     |

| 상세내역                                                                                         | Synopsis                                                |       |                  |     |

| 주저자                                                                                          | 김                                                       | 공동저자  | 김                |     |

| 발행일                                                                                          | 2017-01-16 페이지(시작-끝)                                    |       |                  |     |

| <a href="#">Download</a> Algorithm for Synthesis and Exploration of Clock Spines.pdf(131 Kb) |                                                         |       |                  |     |

- JICAS Citation

- 참여교수 실적에 등록한 논문 중 JICAS 내용을 인용한 논문 실적 인정

- 성과 : 논문 게시판에 논문 등록 및 인용 여부 선택

성과 : 논문

국외/국내  SCI구분

학회/저널  논문집명

IDECA지원여부  지원내역

상세내역

지원 문구 기재 페이지

JICAS Citation  \*\* JICAS 논문을 Reference 내 기재한 경우만 해당

주저자  공동저자

발행일  페이지(시작-끝)

논문제목

논문첨부  선택된 파일 없음

## • IP(입력 항목 화면)

**성과 :: IP**

“한국 반도체산업의 경쟁력”

IDECA에서 설계인력양성의 발판을 마련하겠습니다.

IP Name Low drop out (LDO) regulator in FlexRay Communication 등록일 2016.10.18 11:39

이름 학교명

IP Code KU423H0796 등록기관 KIPEX

거래수 1 등록일 2016-04-29

IDECA지원여부 IDECA지원 지원내역 MPW

상세내역 매그나칩반도체/SK하이닉스 180nm

Category Analog

[\[DOWNLOAD\]](#) Low drop out %28LDO%29 regulator.docx(54 Kb)

KU423H0796 / Register

IP Code : KU423H0796 | IP 등록일 : 2016-04-29 | 승인일 : 2016-05-12 15:08:31 | 수정하기

IP Name Low drop out (LDO) regulator in FlexRay Communication

IP Version 1.0

Category Analog & Mixed Signal > Amplifier/Filter/Bias Circuit > Voltage Reference

Description The Designed IP is the Low drop out (LDO) in FlexRay communication. The designed IP can

- Low drop out Voltage: 500mV

- Output Current: 1.3mA

- Wide range of supply voltage(2.8V~6V) and temperature(-40°C~80°C)

- Adjustable Output

Foundry Magnachip Semiconductor

Technology 0.18um  $\pm$  < 0.25um

IP Type Hard IP

Format Spice

Silicon Verification Status 개발결과

적용된(될) Chip의 Function LDO regulators are used to derive lower output voltages from a main supply or battery. They

- Power management IC, Voltage monitor etc.

적용된(될) Chip의 Application This IP can be applied to variety of chips which is demanded using the various supply

BIZ 범위 1. 전 산업용 반도체

2. 물자류, 가동장비

3. 전자제품, 소비자제품

## • 특허(입력 항목 화면)

**성과 :: 특허**

“한국 반도체산업의 경쟁력”

IDECA에서 설계인력양성의 발판을 마련하겠습니다.

특허명 MULTI-REFERENCE CORRELATED DOUBLE SAMPLING DETECTION METHOD AND 등록일 2016.10.24 19:12

이름 학교명 KAIST

국제/국내 국제 출원/등록 출원

출원번호 CN-201610847293.6 등록일 2016-10-24

IDECA지원여부 IDECA지원 지원내역 MPW

상세내역 매그나칩반도체/SK하이닉스 350nm

[\[DOWNLOAD\]](#) P-13487-CN(OP2016-055) 출원서류 (1).pdf(1 M)

기존의 열전 냉각기 및 기계적 센터를 제거할 수 있는

전기적 센터를 회로 동작을 통해 구현함으로써, 획기적으로

모듈 비용을 감소 시킬 뿐만 아니라, 낮은 동작 운도를 보장하며,

이를 자유롭게 조정할 수 있음.

[\[목록\]](#) [\[쓰기\]](#) [\[수정\]](#) [\[삭제\]](#)

## ③ 신청내역 확인 및 수정

- 마이페이지 → 참여교수 신청내역에서는 지금까지 참여한 참여교수 신청 상세 내역을 확인 할 수 있으며 지도학생 수정 및 인력배출현황 기입 가능

| 제목            | 활동기간                    | 신청일자       | 상태        |

|---------------|-------------------------|------------|-----------|

| 2025년 참여교수 신청 | 2025-02-19 ~ 2026-02-28 | 2025.02.03 | 결과보고 제출기간 |

| 2024년 참여교수 신청 | 2024-03-01 ~ 2025-02-16 | 2024.02.01 | 마감        |

| 2023년 참여교수 신청 | 2023-03-01 ~ 2024-02-29 | 2023.02.01 | 마감        |

| 2022년 참여교수 신청 | 2022-03-01 ~ 2023-02-28 | 2022.02.04 | 마감        |

- 참여교수 신청내역의 상세 페이지를 보면 실적산정기간 중 달성한 실적과 실적별 배점기준에 따라 부여한 점수가 보여지고 해당 점수를 클릭하면 상세 내역도 확인 가능

| 신청기간                    | 신규참여교수 평가               | 활동기간                    | 결과보고 제출기간               |

|-------------------------|-------------------------|-------------------------|-------------------------|

| 2025-02-03 ~ 2025-02-28 | 2025-02-17 ~ 2025-03-19 | 2025-02-19 ~ 2026-02-28 | 2025-12-01 ~ 2026-02-28 |

| 신청정보상세                                          |  | 결과보고 제출                                         |    |

|-------------------------------------------------|--|-------------------------------------------------|----|

| 2025년 참여교수 신청                                   |  | [Congress 참여] 2025 IDEC Congress(2025.07.03) 참여 |    |

| [Congress 참여] 2025 IDEC Congress(2025.07.03) 참여 |  | 1                                               | 10 |

|                                                 |  | 2025.09.04                                      |    |

|                                                 |  | 총계: 10                                          |    |

## ※ 학회 및 저널 등급표

| 구분       | 등급 | 내용                                                                                                                                                                           |

|----------|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 학술<br>대회 | A  | ISSCC / Symposium & VLSI circuit and Technology(SOVC) / CICC                                                                                                                 |

|          | B  | DAC / ICCAD / ASSCC / IEEE RFIC Symposium / ESSCIRC                                                                                                                          |

|          | C  | ISCAS / ASP-DAC / COOLCHIPS / BIOCAS / EMBC / HOTCHIPS                                                                                                                       |

|          | D  | 기타 국제 학회                                                                                                                                                                     |

| 저널       | A  | IEEE TCAS I / IEEE TCAS II/ IEEE JSSC / IEEE Transaction on Electron Devices/ IEEE Transaction On CAD / IEEE Transactions on Microwave Theory and Techniques (*또는 이에 준하는 저널) |

|          | B  | A등급외 관련분야 IEEE 저널(단, IEEE Transactions on Consumer Electronics는 제외) / ACM / SCI-E                                                                                            |

|          | C  | 기타 국제 저널                                                                                                                                                                     |

|          | D  | 국내 저널                                                                                                                                                                        |

## 9. 우수 참여교수 선정

- 1) 5년 이상 활동한 참여교수 중, 최근 1년 동안 참여활동이 우수한 교수를 선정하여 시상

- 2) 선정 방법

- ① 최종 산출된 실적 점수를 근거로 상위 점수자를 선정(최대 2~3명)

- ② 해당 실적 : IDEC 참여 실적, 논문실적(IDEC 사사문구가 들어간 논문만 해당)

- ③ 점수 산출 방법

- IDEC 참여실적 점수와 논문실적 점수의 비율 = 2:1 적용

- 위 비율 적용된 값의 총합계 산출

- 선정 제외 대상 : 최근 2년간 수상자, 수상 대상자 중 불참자

- ④ 참여교수 운영위원 검토 후 최종 선정

- 3) 시상 : IDEC Congress 개최 시 『우수 기여상』 시상(연 1회, 6~7월)

## 10. 우수 연구교수 선정

1) 당해연도 참여교수 실적인정 논문을 바탕으로 상위 2 명 내외 선정

2) 선정 방법

- ① 최근 3년간 A급 학술대회 발표 및 A급 저널 논문 15편 이상(사사문구가 기입된 논문만 심사 대상으로 함)

- ② 최근 3년간 우수 연구교수 수상자 제외

- ③ 기준에 부합하는 대상자가 없을 경우, 그 해는 수여하지 않음.

\* 참고\_논문 실적 배점기준표

| 등급      | 배점 | 학회명                                                                                                                                                      |

|---------|----|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| A급 학회논문 | 15 | ISSCC, Symposium & VLSI circuit and Technology(SOVC) , CICC                                                                                              |

| B급 학회논문 | 7  | DAC, ICCAD, ASSCC, IEEE RFIC Symposium, ESSCIRC                                                                                                          |

| C급 학회논문 | 4  | ISCAS, ASP-DAC, COOLCHIPS, BIOCAS, EMBC, HOTCHIPS                                                                                                        |

| D급 학회논문 | 2  | 기타 국제학회                                                                                                                                                  |

| A급 저널논문 | 15 | IEEE TCAS I, IEEE TCAS II, IEEE JSSC, IEEE Transaction on Electron Devices IEEE Transaction On CAD, IEEE Transactions on Microwave Theory and Techniques |

| B급 저널논문 | 7  | A등급외 관련분야 IEEE 저널(단, IEEE Transactions on Consumer Electronics는 제외), ACM, SCI, SCI-E                                                                     |

| C급 저널논문 | 4  | 기타 국제저널                                                                                                                                                  |

| D급 저널논문 | 2  | 국내저널                                                                                                                                                     |

3) 시상 : IDEC Congress 개최 시 『우수 연구상』 시상(연 1회, 6~7월)

## 1. MPW 참가 대상 및 설계 참여시 이행 사항

### 1) 개요

- ① MPW(Multi-Project Wafer)는 대학의 칩제작 지원 프로그램으로 국내 전문설계인력 양성을 위해 특성별 공정 지원으로 운영됨.

- ② 창의적인 아이디어를 실제 칩으로 구현할 수 있는 기술 지원을 제공하여 실질적인 교육 및 연구 지원. 또한 칩제작비를 직접 지원하여 설계할 수 있도록 지원함.

- ③ Layout 과정까지 수행되던 교육 및 연구를 실제 chip의 제작, 시험, 응용까지 연계시킴으로써 설계능력을 갖춘 고급 인력 양성이 가능하도록 함.

- ④ 1996년부터 시행하였으며, 매년 300여개의 칩제작 지원함.

### 2) 참여 조건

- ① 참가 대상 : IDEC 참여교수로 협약서 체결이 완료된 대학교의 연구실

- ② 신청 조건 : 최근 2년간 논문실적(사사문구 포함)이 있을 경우 참여 가능

| 구분    | 1. 지정공정(삼성 28nm, 130nm 공정)                                                             | 2. 희망공정(DB 180nm)                     |

|-------|----------------------------------------------------------------------------------------|---------------------------------------|

| 인정 범위 | <b>IDEC MPW 참여 인정 논문 중 학회/저널 A/B/C 등급에 2년간 1편 이상 게재한 경우</b>                            | 아래 학회 및 저널 중 A/B 등급에 2년간 1편 이상 게재한 경우 |

| 비고    | 3년 이내 임용된 신임교수는 실적이 없어도 참여 가능함.(2023년 이후 임용)<br>(** 실적 업로드 : IDEC 홈페이지 - 참여교수 - 성과:논문) |                                       |

#### [참고] IDEC MPW 참여 인정 논문 (학회 및 저널)

##### [※ 학회]

A 등급 : ISSCC, Symposium & VLSI circuit and Technology(SOVC) , CICC

B 등급 : ICCAD, DAC, ASSCC, IEEE RFIC Symposium, ESSCIRC

C 등급 : ISCAS, ASP-DAC, COOLCHIPS, BIOCAS, EMBC, HOTCHIPS

##### [※ 저널]

A 등급 : IEEE Transactions on Microwave Theory and Techniques, IEEE Transaction On CAD, IEEE TCAS I, IEEE TCAS II, IEEE JSSC, IEEE Transaction on Electron Devices

B 등급 : A등급외 관련분야 IEEE 저널(단, IEEE TCE는 제외), ACM, SCI-E

C 등급 : 기타 국제저널

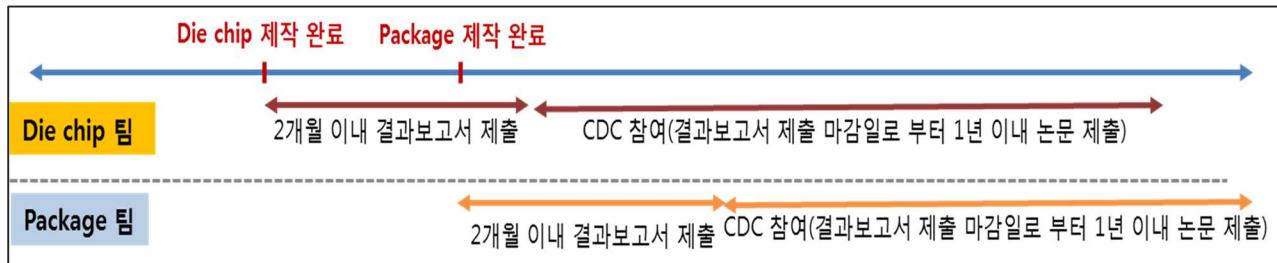

## ③ MPW 참가 내역에 대한 의무사항 이행 완료팀 (\*신청전 확인해 주세요.)

| 구분      | 의무사항                                                           | 삼성 공정 | (희망)DB 공정                                                                                                                                                                                                                                                                                                                                           | (희망)해외 공정 |                |        |                                                                |         |                                                                |  |

|---------|----------------------------------------------------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|----------------|--------|----------------------------------------------------------------|---------|----------------------------------------------------------------|--|

| 공통      | IP 소개서 제출                                                      |       | Tape out 제출시 web에 작성(마이페이지)                                                                                                                                                                                                                                                                                                                         |           |                |        |                                                                |         |                                                                |  |

|         | 결과보고서 제출                                                       |       | 칩제작 완료 후 2개월 이내 제출                                                                                                                                                                                                                                                                                                                                  |           |                |        |                                                                |         |                                                                |  |

|         | Chip Design Contest(CDC) 참여                                    |       | 칩제작 완료 후 1년 이내 참여(포스터 및 발표영상)                                                                                                                                                                                                                                                                                                                       |           |                |        |                                                                |         |                                                                |  |

| 희망 공정   | JICAS 논문 게재                                                    | -     | <p>* 칩제작 완료 후 1년 이내 제출(*대체 참여 가능)</p> <table border="1"> <thead> <tr> <th>구분</th><th>JICAS 제출 대체 조건</th></tr> </thead> <tbody> <tr> <td>~2024년</td><td>연구실내 학회 및 SCI(E) 저널 2 편에 3회 이상을 제출한 실적이 있을 경우 - 1회 의무사항 대체로 인정</td></tr> <tr> <td>2025년 ~</td><td>연구실내 학회 및 SCI(E) 저널 3 편에 5회 이상을 제출한 실적이 있을 경우 - 1회 의무사항 대체로 인정</td></tr> </tbody> </table> | 구분        | JICAS 제출 대체 조건 | ~2024년 | 연구실내 학회 및 SCI(E) 저널 2 편에 3회 이상을 제출한 실적이 있을 경우 - 1회 의무사항 대체로 인정 | 2025년 ~ | 연구실내 학회 및 SCI(E) 저널 3 편에 5회 이상을 제출한 실적이 있을 경우 - 1회 의무사항 대체로 인정 |  |

| 구분      | JICAS 제출 대체 조건                                                 |       |                                                                                                                                                                                                                                                                                                                                                     |           |                |        |                                                                |         |                                                                |  |

| ~2024년  | 연구실내 학회 및 SCI(E) 저널 2 편에 3회 이상을 제출한 실적이 있을 경우 - 1회 의무사항 대체로 인정 |       |                                                                                                                                                                                                                                                                                                                                                     |           |                |        |                                                                |         |                                                                |  |

| 2025년 ~ | 연구실내 학회 및 SCI(E) 저널 3 편에 5회 이상을 제출한 실적이 있을 경우 - 1회 의무사항 대체로 인정 |       |                                                                                                                                                                                                                                                                                                                                                     |           |                |        |                                                                |         |                                                                |  |

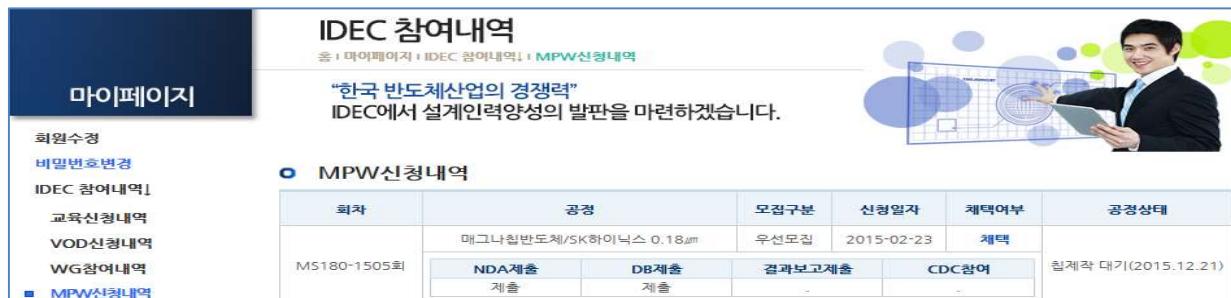

## [참고] 의무사항 이행 여부 확인 방법 :

MY IDEC

MPW신청내역

홈 | MY IDEC | MPW신청내역

○ MPW 신청내역

| 회차          | 공정                                                                                                                                                                                                                                        | 모집구분  | 신청일자       | 채택여부  |        |       |    |    |  |  |  |  |    |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|-------|--------|-------|----|----|--|--|--|--|----|--|--|--|

| SS28-2402회  | 삼성전자 28nm(LPP)                                                                                                                                                                                                                            | 정규모집  | 2024.06.20 | 채택    |        |       |    |    |  |  |  |  |    |  |  |  |

|             | <table border="1"> <thead> <tr> <th>NDA제출</th> <th>DB제출</th> <th>칩 수령</th> <th>결과보고제출</th> <th>CDC참여</th> <th>결제</th> </tr> </thead> <tbody> <tr> <td>제출</td> <td></td> <td></td> <td></td> <td></td> <td>미납</td> </tr> </tbody> </table> | NDA제출 | DB제출       | 칩 수령  | 결과보고제출 | CDC참여 | 결제 | 제출 |  |  |  |  | 미납 |  |  |  |

| NDA제출       | DB제출                                                                                                                                                                                                                                      | 칩 수령  | 결과보고제출     | CDC참여 | 결제     |       |    |    |  |  |  |  |    |  |  |  |

| 제출          |                                                                                                                                                                                                                                           |       |            |       | 미납     |       |    |    |  |  |  |  |    |  |  |  |

| CD120-2401회 | 삼성전자 삼성 130nm BCDMOS                                                                                                                                                                                                                      | 정규모집  | 2024.06.20 | 채택    |        |       |    |    |  |  |  |  |    |  |  |  |

④ **취소팀 패널티 적용(2024년부터 적용)**

| 취소횟수(년기준)                   | 1회                                      | 2회          | 3회 이상      |

|-----------------------------|-----------------------------------------|-------------|------------|

| 참가신청 제한<br>(취소년도의 다음해 적용)   | 차년도 MPW 신청 제한 3개월<br>(2~4월 모집팀(마감일 기준)) | 1년          | 2년 참여 불가   |

| 예) 2024년 취소시<br>2025년 적용 조건 | 2025년 2~4월                              | 2024년 모집 전체 | 2024~2025년 |

- ⑤ 반드시 교육 및 비상업적 연구 목적으로만 제작 참여해야 함.

- ⑥ 이외 목적으로 참여한 것이 확인될 경우 참여교수 지원이 중단됨.

### 3) MPW 참가시 의무 이행 사항 (세부 설명)

: 해당 내용을 모두 이행하여야 차년도 MPW 참여 신청이 가능함.

#### [ 공통 ]

##### ① Rule file 관리 의무

- 설계를 위해 배포된 Design rule file은 NDA 작성한 연구실 담당자만 사용 가능

- 해당 설계 외 사용 및 외부 유출이 되지 않도록 철저한 보안유지

- 관리 소홀로 외부 유출이 될 경우 법적 책임이 주어지며, IDEC 참여교수 활동 제한함.

- 설계를 위해 배포된 Design rule file은 NDA 작성한 연구실의 지도교수와 설계참여자만 사용 가능

##### ② IP 소개서 제출

- Tape out 제출시 web에 작성(마이페이지)

##### ③ 결과보고서 제출(칩제작 완료 후 2개월 이내 제출)

- 영문 4-5쪽 이상으로 작성하여 제출

- 설계 검증 결과를 포함하여 작성

##### ④ 결과 발표(IDECK Chip Design Contest) : 칩제작 완료 후 1년 이내 참여

- 논문 제출 및 데모(패널) 전시

- CDC 개최 학회

: KCS(1-2월중 개최), IDEC Congress(7월 개최), ISOCC(10-11월 중 개최)

##### ⑤ MPW 참여시 이전 참여한 MPW 중 이행하지 않은 내역이 있을 경우 참가 신청이 되지 않음. (연구실 단위로 적용됨.)

#### [ 희망공정 설계팀 ] – 기존 지원 받은 해외희망공정팀 포함.

##### ① JICAS 게재 의무 : 칩제작이 완료된 후 1년 이내 제출

- 내용 : 설계 참가시 작성된 내용을 기반으로 작성하는 것이 원칙임.

- JICAS 참여 대체 조건(2021년 희망공정 참여팀부터 적용) : 해당 학회 및 저널에 논문 기재된 경우

- **(★)JICAS 제출 대체 방법** : 해당 연구실의 논문 작성시 JICAS 를 Citation(Reference 항목 추가)한 실적으로 대체 가능

| 년도              | JICAS 제출 대체 조건                                                               | 비고                                                                                       |

|-----------------|------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 2021년<br>~2024년 | <u>연구실내 학회 및 SCI(E) 저널 2 편에<br/>3회 이상을 제출한 실적이 있을 경우</u><br>- 1회 의무사항 대체로 인정 | 논문 2 편 이상이 작성되어야 하며, citation은 1 편에 최소 1회, 최대 2회까지 인정함.<br>단, 3회 이상의 실적은 연구실의 자체 실적으로 인정 |

| 2025년~          | <u>연구실내 학회 및 SCI(E) 저널 3 편에<br/>5회 이상을 제출한 실적이 있을 경우</u><br>- 1회 의무사항 대체로 인정 | 논문 3 편 이상이 작성되어야 하며, citation은 1 편에 최소 1회, 최대 2회까지 인정함.<br>단, 5회 이상의 실적은 연구실의 자체 실적으로 인정 |

- **대체 논문 등록 방법** : IDEC 홈페이지 – 교수님 login – 참여교수 – 논문등록

- 등록시 'JICAS 대체 클릭'(상시 등록 가능), 담당자에게 실적 입력 요청

이메일 발송하기(조일선 주임, ilsun@kaist.ac.kr)

#### 4) 관련 양식 다운로드, 작성 페이지

- ① 설계회로설명서 : 홈페이지 MPW 참여안내 – MPW Flow(1번항목) 다운로드

- ② 결과보고서 : 홈페이지 MPW 참여안내 – MPW Flow(9번항목) 다운로드

- ③ 수정신청 :: MYIDE – MPW/희망공정 – 해당회차 – 수정신청

- ④ IP 소개서 제출 (layout 사진 + IP 내용 10줄 내외)

: MYIDE – MPW/희망공정 – 해당회차 – DB 제출 클릭 - DB제출서 등록

- ⑤ 결과보고서 제출

: MYIDE – MPW/희망공정 – 해당회차 – 결과보고서 제출

- ⑥ CDC 참여 : 홈페이지 CDC 신청 – 희망 참여 CDC 참여 신청

(\*\* 참여했던 내역은 MYIDEC-CDC에서 확인할 수 있음.)

- ⑦ JICAS 제출 페이지 : [Journal of Integrated Circuits and Systems](#)(바로가기)

- ⑧ 칩수령 신청 : 방문시 해당회차 설계팀에게 보낸 메일의 "수령신청"을 클릭하고 신청

- ⑨ 방문확인서 발급 : 설계자 개인 페이지에서 신청 가능(MYIDEC) – 신청 후 방문여부 확인 후 발급됨.

★ MPW 신청과 의무사항 이행 내역은 참여교수님 ID로

로그인하셔야 제출 및 확인이 가능함.

## 2. 2026년 MPW 지원 내역 및 일정

### 1) 2026년 MPW 지원 내역

① MPW 지원 공정 내역 : 정확한 지원 수와 지원 규모는 2월 말 공지 예정

- **지정공정** : 삼성에서 제작 지원되는 공정으로 모든 설계 환경과 일정은 지정된 내역으로 제작 진행.

=> **4개** 공정(삼성 14nm & 28nm & 130nm) **최대 232개** 칩 제작 지원

- **희망공정** : 제작비를 직.간접적으로 IDEC에서 지원하는 공정

a. (국내)희망공정 : DB Hitek 180nm

=> **년1회 최대 22개** 칩 제작 지원(팀별 약 600만원 제작비 지원)

b. (해외)희망공정 : 지원 중단 예정(2026년)

=> 예산 감액으로 인해 지원을 중단하게 됨.

| 구분               | 회사          | 공정                 | 공정내역                                               | Size<br>(mmx<br>mm) | 칩수<br>/1 회 | 모집<br>횟수 | Package<br>사용 pin<br>수(Design) | Package<br>type |  |

|------------------|-------------|--------------------|----------------------------------------------------|---------------------|------------|----------|--------------------------------|-----------------|--|

| 지정<br>공정         | 삼성          | 14nm               | FinFET                                             | 3.55x<br>3.55       | 48         | 1        | 208pin                         | BGA             |  |

|                  |             | 28nm<br>LPP        | CMOS RF 1-poly<br>8-metal                          | 4x4                 | 48         | 2        | 208pin                         | LQFP<br>208pin  |  |

|                  |             | 28nm<br>FD-SOI     | FD-SOI (Fully<br>Depleted-Silicon on<br>Insulator) | 4x4                 | 48         | 1        |                                |                 |  |

|                  |             | 130nm<br>BCDMOS    | BCD1370HP (~70V)                                   | 3.55x<br>3.55       | 20         | 2        |                                |                 |  |

| (국내)<br>희망<br>공정 | DB<br>Hitek | 180nm<br>BCDMOS    | CMOS 1-poly<br>4-metal TM                          | 5x5                 | 22         | 1        | 지원하지 않음.                       |                 |  |

| (해외)<br>희망<br>공정 | 국내외<br>공정   | <b>2026년 지원 중단</b> |                                                    |                     |            |          |                                |                 |  |

② 지원 공정 세부 내역 확인 방법(아래 창에서 참여 방법과 일정 확인 가능)

**MPW / CDC**

**MPW참여안내**

홈 | MPW / CDC | MPW참여안내

**“한국 반도체산업의 경쟁력”**

IDECK에서 설계인력양성의 발판을 마련하겠습니다.

**MPW참여안내**

- MPW신청

- 희망공정신청

- CDC소개

- CDC신청

- CDC영상

- IP Library

- Soket/Board

- Package업체정보

- 테스트보드업체정보

**MPW(Multi-Project Wafer)**

- 국내 대학(원)에서 시스템반도체 실무설계 능력을 가진 인력 양성을 위해 칩설계에서 제작까지 경험할 수 있도록 기회 제공

- 삼성전자, 매그나칩반도체, SK하이닉스, 동부하이텍, TowerJazz의 칩제작 지원

- Semitea, Amkor 패키지 사업 지원

- 매년 10개 내외의 공정으로 공모전 진행, 300여개의 Chip 제작

- 참여 대상 : IDECK 참여교수/참여학생

**MPW Flow**

## 2) 2026년 MPW 진행 일정

- 회차 표기 방법 변경

: “공정코드-년도모집순서”(예시) 삼성 28nm FD-SOI 2026년 01회차 : SF028-2601)

- **지원 공정은 공정사와 협의 중이며**, 이에 대해 결정이 되면 자세한 일정 안내 가능함.

- 아래 일정 및 지원 내역은 최종 확정 전으로 조정 가능함. (\*\*2월 말 확정)

- 모집 : 모집 마감 2주전부터 접수

- 선정 결과 : 모집 마감 후 20일내 개별 통보

- Package 제작 지원 공정 : Die out 이후 1개월 소요됨.

- 진행 일정 계획(안)

| 공정                 | 회차구분<br>(공정_년도순서) | 제작칩수 | 모집 및<br>선정 | DB 마감      | Die-out    |

|--------------------|-------------------|------|------------|------------|------------|

| 삼성 14nm FinFET     | SS014-2601        | 48   | 2026.06    | 2027.02.15 | 2027.07.31 |

| 삼성 28nm LPP        | SS028-2601        | 48   | 2026.03    | 2026.07.06 | 2026.12.26 |

|                    | SS028-2602        | 48   | 2026.06    | 2027.01.18 | 2027.07.10 |

| 삼성 28nm FD-SOI     | SF028-2601        | 48   | 2026.04    | 2026.09.07 | 2027.03.10 |

| 삼성 130nm<br>BCDMOS | SB130-2601        | 20   | 2026.03    | 2026.07.06 | 2026.11.30 |

|                    | SB130-2602        | 20   | 2026.05    | 2026.12.01 | 2027.04.30 |

| 공정                       | 회차구분<br>(공정_년도순서) | 제작칩수 | 모집 및<br>선정 | DB 마감      | Die-out    |

|--------------------------|-------------------|------|------------|------------|------------|

| DB Hitek 180nm<br>BCDMOS | DB180-2601        | 22   | 2026.03    | 2026.07.20 | 2026.12.10 |

3) MPW 지원 공정별 내역 정리

- 공정별 진행 절차

| 공정       | NDA체결                           | 설계<br>설명회                 | DB 제출<br>(IP소개서)                             | Fab out                                                                       | 결과보고서/CDC<br>참여 | JICAS                                                                               |

|----------|---------------------------------|---------------------------|----------------------------------------------|-------------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------------------|

| 삼성       | 14nm<br>&<br>28nm<br>&<br>130nm | 설계팀-삼<br>성간 계약            | 선정 후<br>4주 이내<br>개최<br>(온라인<br>제공 필<br>수 구독) | 1차)<br>DB 제출서<br>(IP<br>소개서)<br>작성(Web)<br>2차)<br>설계데이터<br>제출(DB-지<br>정된 Ftp) | IDECK에<br>서 배포  | (전체동일)<br>결과보고서 – 칩<br>제작 후 2개월<br>이내 제출<br><b>CDC</b> – 칩 제작<br>완료일 기준 1년<br>이내 참여 |

| DB Hitek | 180nm<br>BCD                    | 설계팀-공<br>정사-IDECK<br>간 체결 |                                              |                                                                               |                 | 우수팀에<br>제출 요청<br><br>제출 의무<br>- 칩수령후<br>1년 이내<br>(*대체가능)                            |

- 참가비(\*2024년 기준이며, 최종 지원 기준은 2월 중 공지)

| 구분       | 공정 |             | 참가비                                                    |  | 참가신청                                  | 선정평가구분                 |

|----------|----|-------------|--------------------------------------------------------|--|---------------------------------------|------------------------|

| 지정<br>공정 | 삼성 |             | 14nm FinFET<br>28nm LPP<br>28nm FD-SOI<br>130nm BCDMOS |  | ★미정 : 지원에 필요<br>한 예산에 맞춰 배정<br>할 예정임. | 설계회로<br>설명서<br>(4쪽 내외) |

| 희<br>망   | 국내 | DB<br>Hitek | 180nm BCDMOS                                           |  |                                       | 모집팀수 ><br>제작가능수        |

### 3. MPW 참여 방법

#### 1) 참여 대상 및 준비사항

- ① 참여 가능 대상자 : IDEC 참여 대학 협약서 체결이 완료된 대학교의 연구실로 최근2년간 IDEC 지원 사사문구가 포함된 학회 및 저널에 게재한 논문 실적이 있는 경우 신청이 가능함.(해외 희망공정의 경우는 국제학회 및 저널 실적이 있어야 지원이 가능함.)

- ② **설계회로설명서**(설계계획서로 사전 작성하여 신청 시 첨부해야 함.)

- 공정사 제출 및 평가 자료로 활용(설계 내용과 동일해야 함.)

- 국문 또는 영문으로 4쪽 이상으로 작성.

- **설계회로설명서 양식 및 작성요령**(\*IDEC 홈페이지-MPW-MPW참여안내 다운로드)

- ③ 삼성 공정 설계 참여팀은 IDEC 클라우드 서버를 접속하여 설계 진행

- 서버 접속 : NDA 계약 체결자(지도교수와 실설계자 – 참여신청 설계명단)

- IDEC 클라우드 서버 접속 방법 등 관련 안내 : 선정팀에게만 별도 안내함.

#### 2) 진행 절차(Flow)

설계자 모집

- 참여 대상 : 참여교수

- 모집 : 정규모집으로 진행

- 제출서류 : 설계회로설명서(국문 또는 영문 : 4~5쪽)

#### [모집별 운영 방법]

| 모집구분   | 모집                                                                     |

|--------|------------------------------------------------------------------------|

| 모집팀수   | 제작 가능 칩 수의 100% 이내 모집(*미달시 추가모집 진행)                                    |

| 선정방법   | 삼성공정 : 모집팀수>제작 가능 수 =>의 경우 평가로 선정<br>이외 공정 : 모든 참여팀을 평가하여 제작 지원팀을 선정함. |

| 설계설명회  | 회차별 개최(선정 후 4 주 이내 개최) 또는 온라인 자료 제공                                    |

| NDA 체결 | 선정 안내 후 제출(지정공정 : IDEC을 통한 일괄 체결, 희망공정 : 설계팀의 개별 체결)                   |

| 모집구분             | 모집                                                                                                                                                                                                                                                        |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Design Kit(DK)배포 | <p><b>지정공정</b>) NDA 제출 이후 IDEC에서 일괄 배포(수령 방법은 채택 통보시 안내)</p> <ul style="list-style-type: none"> <li>· M/S 공정 및 DB Hitek 공정: ftp를 통해 데이터 수령</li> <li>· 삼성공정 : IDEC 클라우드 서버 접속으로만 사용 가능</li> </ul> <p><b>희망공정</b>) 설계팀이 NDA 체결 후 직접 수령, 체결 업체를 통해 제공받음.</p> |

| 참가비 납부 (지정공정)    | 선정 안내 후 1개월 이내 납부 완료                                                                                                                                                                                                                                      |

선정 평가

- 진행 : 모집마감 후 20일내 선정 완료

- 대상 : 참여팀에 대해서는 모두 평가를 통해 지원팀 선정(단, 삼성공정은 신청팀이 미달할 경우 평가없이 모두 제작 기회 제공)

[선정 절차]

접수 마감

- 정규모집 미달 시에만 추가 접수 진행

회로설명서 확인

- 제시한 양식에 맞춰 작성 여부를 확인함.

- 수정기간 : 마감후 4 일 이내

선정 평가 진행

- 1) 1연구실 1개칩을 기준으로 우선 적용하여 순위에 따라 선정

- 2) 참여팀에 대해서는 모두 평가를 통해 지원팀 선정(단, 삼성공정은 신청팀이 미달할 경우 평가없이 모두 제작 기회 제공)

선정 결과 발표

- 마감 후 20 일 이내 결과 공지

NDA접수 & PDK배포

- 대상 : 선정된 설계팀(지정공정 설계 참여팀)

- NDA 접수 : 선정 후 10일이내 접수(공정별 차이가 있음.)

- 데이터 제공 : NDA 접수 후 Ftp(또는 서버 제공)를 통해 제공함.

[공정별 NDA 체결 방법]

| 구분      | DB Hitek 공정         | 삼성 공정                                    |

|---------|---------------------|------------------------------------------|

| 제출방법    | 공정사가 제공한 양식으로 작성    |                                          |

| 계약체결 대상 | 설계참여대학 - 공정사 - IDEC | 설계참여대학 - 공정사<br>(IDECK은 각 학교의 대리인 역할 수행) |

|           |                                   |                                                      |

|-----------|-----------------------------------|------------------------------------------------------|

| 제출시기      | 선정 완료 후 15일내(공정사의 양식검토로 지연될 수 있음) |                                                      |

| PDK 제공 방법 | FTP를 통해 다운가능                      | IDECK 클라우드 서버에 위치<br>-서버 접속하여 설계진행                   |

| PDK 제공 시기 | 공정사의 NDA 승인 후 제공(NDA 마감 후 10일이내)  | 공정사의 NDA 승인 후 접속하여 설계 가능                             |

| 비고        |                                   | NDA는 각 학교별 계약 체결.<br>총장(또는 산학협력단장)의 직인 날인-설계팀에 별도 안내 |

설계설명회

개최

- 대상 : 지정공정)선정된 설계팀 중 NDA 제출팀 참여 가능함. 설명회 참여 또는 제공된 시청각 자료를 시청해야 PDK를 제공함

희망공정)설계설명회가 개최되지 않음.

- 개최 : 지정공정은 선정 후 4주 이내(희망공정은 개최하지 않음)

- 참여의무 : 1개팀 1인 이상 참여(단, 해당년도 1회 이상 참석자는 제외)

참가비

납부 및

지원

- 삼성 & DB 공정 : 참가비 납부를 선정 후 30일 이내해야 함.

- (해외)희망공정의 경우 : 설계팀이 공정사로부터 받은 견적서를 제출하면 IDECK 지원 금액을 확인하여 견적서를 발행해서 제출해 야함. (fab in 6주 전)

- 지원 절차 : 해당 설계팀에게 개별 연락하여 해당업체에 칩제작비 지원

DB 접수

(지정공정)

- DB 제출 안내 : 제출일 4주전 공지

- DB 접수

- 1)Web-DB제출 검증(DB공정 제외) 2)Web-DB 제출서 작성 3)Ftp DB 업로드(삼성공정은 클라우드 서버)

- 팀별 Device Logo 및 Login account No. 지정

- DB 제출시 : IP개요 및 Layer 사진도 업로드 해야 제출 가능함.

### DB 검토

- DB 검토 : 접수 후 2주~4주 내 검토하여 공정사 전달

- 검토 진행 : 담당 연구원(삼성 및 DB 공정)

- 희망공정은 설계팀에게 개발 검증

- DB Hitek 공정 : 제시된 ftp에 제출

- 삼성 공정 : 1~2주전부터 검토 작업 후 머지 진행

- 희망 공정 : 설계팀 내에서 자체 검증하여 제출

### 결과보고서 /NDA폐기확인서 인서 제출

- 제출 : 칩 제작완료 일로부터 2개월내

- 방법 : Web에서 제출

- 결과보고서: 영문 5쪽 이상으로 작성

- NDA 폐기확인서: 모든 설계팀 서명 필수(결과보고서 제출시)

### CDC 참여

- 3회 개최 : 한국반도체학술대회(1-2월), IDEC Congress(6월), ISOCC(10-11월)

- 참여 방법 : 논문 제출, 전시 참여(데모 또는 패널)

- 설계팀은 포스터 및 발표 영상을 업로드해야 함.

### JICAS 논문제출

- 설계전문학술지 : 논문 제출

- 희망공정은 제출 의무(제작완료 후 1년이내 제출, 대체 논문 가능)

## 4. 참여방법(지정공정)

### 1) 설계 참여팀 사전 준비 사항

- 설계회로설명서(설계계획서로 사전 작성하여 신청 시 첨부)

- 설계 내용 확인 및 평가시 자료로 활용(설계 내용과 동일해야 함.)

- 내용 구성 : 설계회로설명, 기존회로와의 비교, 회로설계방법, Simulation, 설계정보, 칩 검증 방법, 설계면적에 대해 내용 기재

- 국문(또는 영문) 4~5 쪽으로 작성(2016년 MPW부터 적용)

- 회로설명서 양식 및 작성요령 파일 다운로드(\*IDECK 홈페이지/MPW/참여안내)

- 삼성 공정 설계는 IDECK 클라우드 서버로 접속해서만 설계가 가능함.

- 접속 방법은 설계 참여자에게 별도 안내

### 2) 신청 확인

- 지도교수 ID – 마이 페이지에서 확인

- 접수 기간 내에만 수정/취소 가능(평가전까지는 직접 수정 가능)

- 평가 진행 후는 마이페이지에서 수정/취소 신청을 해야 함. 직접 수정이 아닌 메일로 내용이 전달되도록 함.

(취소기간에 따라 패널티 적용 범위가 다름.(참가비 항목 참조))

#### ① 신청서 수정 방법

- 모집 기간 내 수정

- 마이페이지에서 내역을 수정할 수 있음.

- 예외) 경쟁률이 높아 평가 진행되는 회차는 평가 준비 기간 내도 수정 가능함.

- 모집 기간 후 수정

- 마이페이지 – 수정 – 메일로 전달 – 이후 수정 처리됨. (아래 그림 참조)

○ SS28-2202회 삼성전자 28nm (정규모집)

| 신청기간                    | 평가기간                    | 선정발표       | NDA 제출기간                | 결제기간                    | DB 제출기간                 | Die-out Package       | 결과보고 제출기간               |

|-------------------------|-------------------------|------------|-------------------------|-------------------------|-------------------------|-----------------------|-------------------------|

| 2022-04-25 ~ 2022-05-16 | 2022-05-20 ~ 2022-05-29 | 2022-05-30 | 2022-05-30 ~ 2022-06-23 | 2022-05-30 ~ 2022-06-30 | 2022-12-26 ~ 2023-01-16 | 2023-07-10 2023-08-10 | 2023-07-11 ~ 2023-09-10 |

| 신청 정보 상세                | 교육VOD                   | DB제출       | 수정신청                    | 클라우드서버신청                |                         |                       |                         |

○ 이메일 수정신청

|      |                                                                                       |     |           |

|------|---------------------------------------------------------------------------------------|-----|-----------|

| 회차   | SS28-2202(정규모집)                                                                       | 공정명 | 삼성전자 28nm |

| 이름   | 김철우                                                                                   | 학교명 | 고려대학교     |

| 회로제목 | A Multi-Phase Interleaved Synchronous Quasi-Digital LDO with Adaptive Sampling Scheme |     |           |

▣ 수정내용(자세하게 기재해주세요)

- 설계 참여 학생 추가의 경우 교과과정, 현재 학기를 입력해주세요

| 수정 전 내용                                 | 수정 희망 내용                                            |

|-----------------------------------------|-----------------------------------------------------|

| 예시1) Package BGA type<br>예시2) 설계자 추가 희망 | 예시1) Package LQFP type으로 변경희망<br>예시2) 000 석사 3학기 추가 |

이전으로

제출

## 3) 설계팀 선정

### ① 채택확인

- 지도교수 ID - 마이 페이지에서 확인

- 선정 안내 : 마감 후 15일내 선정 안내함. (평가 진행 시 다소 선정이 지연될 수 있음.)

- 선정 방법 : 경쟁률이 높은 경우 아래의 기준으로 평가 진행하여 선정함.

- 많은 설계팀이 참여가 가능하도록 효율적 설계 면적 활용에 배점을 추가하여 평가 진행.

### ② 설계팀 선정

#### 접수 마감

- 정규모집 미달 시에만 추가모집 진행

#### 회로설명서 확인

- 제시한 양식에 맞춰 작성 여부를 확인함.

- 수정기간 : 마감후 4일이내

#### 선정 평가 진행

- 삼성공정)참여팀수<지원수 : 평가 진행(선정 절차대로 진행)

- 삼성공정 외)모든 팀 평가로 선정함.

#### 선정 결과 발표

- 마감 후 15일 이내 결과 공지

#### - 선정 절차

- 1 연구실 1 개침을 기준으로 우선 적용하여 순위에 따라 선정

- 설계 면적 재조사를 통해 전체 면적 조정

- ①~② 적용으로 조정이 이뤄지지 않을 경우 평가로 결정

## • 평가 진행 기준

★ 평가 자료 : 설계회로설명서(평가 시는 소속, 대학, 설계자명, 회로제목 삭제하여 수정)

★ 평가위원 : 공정 참여 지도 교수로 위촉

평가위원 참여 연구실에는 평가 가산점 부여

★ 평가 항목 및 배점 내역(100점)(배점 조정 : 2015.2월 모집부터 적용)

- |                      |                                        |            |

|----------------------|----------------------------------------|------------|

| 1) 디자인의 우수성 30점      | 2) 회로설계방법 (단계별로 사용한 CAD Tool 기재 등) 15점 |            |

| 3) Chip수령 후 검증방법 15점 | 4) Design size(공간 활용도) 25점             | 5) 활용계획 5점 |

| 6) 평가위원들의 주관적 점수 10점 |                                        |            |

### ★ 선정 원칙

경쟁률이 높을 경우 '1연구실 1개집'을 기준으로 우선 적용하여 순위에 따라 선정

우선 선정 후 남은 면적에 대해서는 평가 결과에 따라 제작 기회 제공

\*추가 가산점 : 면적을 1/2 또는 1/4로 조정한 경우

4) NDA(Non-disclosure agreement) 접수 및 설계데이터(PDK) 배포(지정공정에 해당됨.)

- ① NDA(Non-disclosure agreement) : 설계시 필요한 PDK(Process Design Kit) 제공을 위해 설계자-공정사(대리: IDEA)간 보안유지협약서

- ② NDA 체결 대상 : MPW 선정 팀

- ③ 공정별 별도 NDA 제출 안내(지정공정에 한함.)

- ④ 공정별 NDA 접수 방법

- 삼성/DB Hitek 공정 : 날인된 원본 우편 접수 - 실사를 통해 PDK 제공

#### NDA 양식 제공

- IDEA-공정사 협약 이후 양식이 제공됨.

- 대학별 양식 제공(삼성)/일괄 양식 제공(DB Hitek)

#### 참여대학에 양식 전달

- 양식과 작성, 제출 방법에 대해 안내함.

- 10 일 이내 제출

- 원본 2부(대학의 기관장 날인)

#### NDA 접수 (IDEA)

- 대학별 제출한 원본 서류 취합하여 삼성 전달

- 전달시 사본 보관

#### 공정사의 최종 접수 (1부 전달)

- 전달 받은 NDA는 최종 승인

- 승인 후 원본 1부를 IDEA에 다시 전달함.

#### 설계팀에 전달

- 전달받은 서류를 대학 담당자에 전달

- NDA 체결

- MPW 참여 대학 – 삼성과 체결(IDEc은 대리인 역할)

- 각 대학의 대표는 기관장으로 한다.(총장 또는 산학협력단장)

- 체결은 대학에서 설계 참여시 진행됨.

- 체결 방법

- 대학에서 날인한 원본 2부를 IDEc에서 접수

- 접수한 서류를 삼성에 전달

- 공정사에서 최종 직인 날인하여 대학별 1부를 IDEc에 발송해 줌

- 발송된 내역은 각 대학 담당자에게 발송해 준다.

- 참고) IDEc에서는 해당 서류의 사본을 보관한다.

- 특이 사항

- 대학별 1년에 1회 체결로 동 대학의 모든 설계팀은 참여 가능. 단, 이외 설계팀은 약식의 NDA 제출을 해야 함.(공정사의 사정에 따라 달라질 수 있음.)

- 계약자는 '참여학교- 공정사'이며, 학교별 NDA 승인은 총장(또는 산학협력 단장)이 해야 함.

- ⑤ 설계데이터(PDK) 배포 방법 및 시기

- 체결 대상 : PDK는 설계에 필요한 데이터로 NDA 체결한 설계팀에게만 전달됨.

- 공정별 배포 방법과 시기에 차이가 있음.

- 해당 데이터는 IDEc에서 보유하며, 설계팀의 보안도 IDEc에서 관리 감독한다.

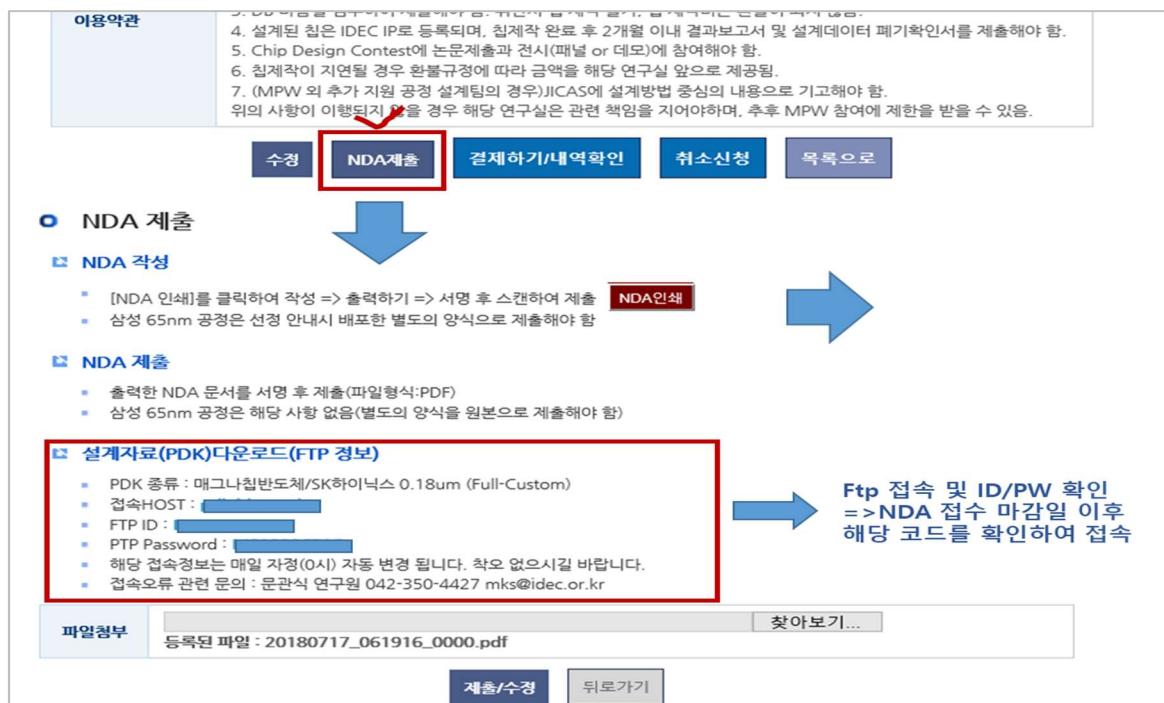

- DB Hitek 공정

- Web에서 접수 – Ftp로 PDK 제공

- Ftp 접속 방법 및 배포

- NDA 접수 마감일 이후 마이페이지-NDA제출(web)에서 접속 Host 및 ID/PW를 확인할 수 있도록 설정됨.

- ID/PW는 매일 변경되며, 데이터 수령시 마이페이지에서 재 확인 필요

- 배포 기간 : NDA 접수 마감일 후 ~ DB 제출 전까지

- PDK 폐기 : 칩 테스트 완료 후 폐기. 또는, 설계 중 제작 포기시(폐기시 반드시 NDA 폐기확인서 제출되어야 함. )

(그림 1)DB 공정 PDK 수령 방법(web)

- 삼성 공정

- IDEC 클라우드 서버에 접속하여 사용 가능함.

- 접속 및 사용 방법은 설계팀별로 안내함.

- 공통) 설계자 추가 시

- 이후 설계자의 추가 참여자가 있을 경우 NDA를 추가 제출해야 함.

- web에서 수정 신청 비고란에 추가자 이름 기재하여 수정 신청함.

- 수정 신청 접수 후 처리 방법을 회신 받으면 NDA를 추가 제출하면 됨.

- 단, 수정 신청하여 설계자는 설계지도교수의 학생으로 web에 등록되어 있어야 함.(등록방법 : 설계지도교수 – 참여교수란에서 학생 추가 가능)

- NDA Design Kit 보안 유지 관련 공지

- 주기적인 공지를 통해 보안에 대해 인식을 강화시킨다.

IDECK의 MPW 참가를 통해 전달받은 Design Kit 일체는 NDA를 통해서 법적인 구속력을 가지며, 관리 소홀로 데이터 유출 시 개인은 물론 소속된 참여교수에도 자격 박탈 등 강력한 규제가 가해질 수 있습니다. 뿐만 아니라 해당 공정사의 이의 제기 시 민, 형사상 책임을 물을 수 있습니다.

MPW 참여자 분들은 Design Kit 및 관련 자료의 관리를 철저히 하시어 불이익을 당하는 일이 없도록 거듭 당부 드립니다.

NDA 체결 후 수령한 Design Kit 일체는 NDA 상에 기재된 폐기 날짜 안에 반드시 폐기하여 주시고 폐기확인서를 제출하여 제3자에 의한 공개 및 유출이 일어나지 않도록 주의 바랍니다.

### 5) 설계설명회 개최(지정공정)

- ① 개최 시기 : 회차별 정규모집 선정 완료 후 1개월 이내 개최

- ② 참여 대상

- MPW 선정팀으로 NDA 제출한 팀 설계자(해당 회차의 설명회 참석해야 함.)

- NDA 제출시 서명한 설계자만 참여 가능함.

- 해당 설계 참여자 1인 이상 반드시 참석해야 함. 단, 같은해 동일공정에 대해 여러 회차 참여시 해당 공정 첫 회만 참석해도 됨.

- ③ 내용 : 공정 설명 및 설계시 유의사항 등

- ④ 자료 배포

- 설계자로 NDA 제출팀에만 제공

- DB Hitek 공정: 온라인으로 진행되며, 해당 자료는 PDK 배포시 함께 제공

- 삼성 공정 : web에서 시청이 가능한 영상 자료 제공. 자료는 서버에서 확인 가능함.

- 참고 사항 : 설명회 영상 및 참여가 확인되어야 PDK 제공이 가능함.

### 6) DB 접수(지정공정)

- ① DB 제출 절차

- DB 공정 : 1)제출서 작성(web) -> DB 제출 ftp ID/PW 확인 가능 =>2)DB 제출 : ftp 업로드

- 삼성 공정 : 1)제출서 작성(web) -> DB 제출 ftp ID/PW 확인 가능 =>2)DB 제출 : 해당 서버에 업로드

- 해외 희망공정 : tape out과 동시에 DB 제출서 및 IP소개서 작성 (web) – 해당 내용 미 기재시 제작비 지원이 필요한 내용임..

- ② 절차 1 : DB 제출서 작성

- 마이페이지 -> IDEC 참여내역 -> 해당 공정 -> 하단 "DB 제출" 클릭하고 작성

- 설계회로설명서와 설계 내용이 상이한 경우 : 최종 설계 내용에 맞게 작성해서 재 제출 요청

- 재제출 방법 : 수정 신청(내용 : 설계회로설명서 변경요청) -> 메일로 전송 -> 내용 수정 처리

- **IP 개요 : 반드시 50~100자 이내로 기재**

- 해당 제출서 작성 후 DB 제출 ftp ID/PW 확인 가능

## ③ 절차 2 : DB 제출 방법

- 접수 기간 : 마감일로부터 20일전부터 접수(공정별 별도 안내함.)

- 제출 Ftp IP : 143.248.230.161

- ID/PW : web에서 DB 제출서 및 IP 등록신청서 작성시 확인

- DB 제출시 확인 사항

- PW는 telnet 접속 후 변경

- PW 변경한 경우 DB 제출 후 재 접속하여 정상적인 제출 확인 필요

- DB 미제출 경우 납부한 칩제작비 환불 불가함.

- DRC 재 검토 시 비용 추가 : DB 검토 오류가 있을 경우 2회부터는 ₩50,000(/회)

- DB 재검토 의뢰서=> 오류가 많아 검토가 지속되면 칩제작 일정이 지연될 수 있어 적용된 패널티 임.(\*양식은 DB 제출 안내문을 통해 전달됨.)

### 7) DB 검토(사전 검증)

- ① 공정별 담당 연구원이 검토는 진행

- ② DB 검토 기간 : 2~4주(공정과 접수 사정에 따라 기한이 조정될 수 있다.)

- ③ 공정별 담당 연구원

|         |                                 |

|---------|---------------------------------|

| 삼성 28nm | 삼성28nm(Analog) / DB Hitek 180nm |

| 김연태 책임  | 조인신 책임                          |

### 8) 칩 배포

- ① 칩제작 기간

- 공정별 12~22주 소요됨

- 제작 기한에 2~3주 전부터 완료일 확인(공정사)

- 제작이 지연될 경우 설계팀에 사유와 제작 예정 일정 공지

- ② 칩 배포 절차

- : IDEC 칩도착 ->설계팀에 안내 ->수령 신청서(web, 설계팀) ->방문하여 수령

- ③ 칩배포 기간 : 제작 완료일 ~ 3주이내

- ④ 칩사진 제공

- 칩사진 -> web에서 받을 수 있도록 업로드

- Web에서 다운 가능(마이페이지 - 신청자 정보(아래 그림 참조))

## ▣ 신청자정보

- 신청 취소는 MPW 담당자에게 문의하시기 바랍니다.

- 첨 사진 다운로드 : S65\_1501\_01\_GILHK.jpg

### ⑤ 칩 배포

- 칩 수령은 직접 수령을 원칙으로 함.(분실 및 파손 우려)

- 칩 수령 전 반드시 수령 신청서를 web에서 작성하고 방문해야 하며, 수령 당사자에게만 배포한다.

마이페이지

회원수정

비밀번호변경

IDECK 참여내역

교육신청내역

VOD신청내역

WG참여내역

**MPW신청내역**

EDATool신청내역

CDC신청내역

JICAS논문투고내역

적립금내역

WG평가

MPW평가

CDC평가

“한국 반도체산업의 경쟁력”

IDECK에서 설계인력양성의 발판을 마련하겠습니다.

**○ MPW신청내역**

| 회차        | 공경                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 모집분       | 신청일자       | 채택여부      | 공경상태                                                               |       |      |    |           |           |           |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|-----------|--------------------------------------------------------------------|-------|------|----|-----------|-----------|-----------|--|--|--|